|

|

Error with Footprint Designer and OrCAD PCB |

Post Reply

|

Page 12> |

| Author | |

chrisa_pcb

Moderator Group

Joined: 29 Jul 2012 Location: San Diego Status: Offline Points: 772 |

Post Options Post Options

Thanks(0) Thanks(0)

Quote Quote  Reply Reply

Topic: Error with Footprint Designer and OrCAD PCB Topic: Error with Footprint Designer and OrCAD PCBPosted: 11 Mar 2014 at 12:25pm |

|

Can you post your FPX along and the details with the exact issue you may have? I'm pretty positive the initial issue was handled but would like to see how its the same or differs from the original issue. Also. make sure to get past a padstack error that you close the error, do file -> save in pad_designer, you should get the error again(close it), it'll ask you to save padstack with warnings.. put yes, and then close it. If you don't manually save a non-plated padstack with warnings, it will not generate the .pad and use the first .pad it can find in the directory rather than the one you wanted it to generate. This will cause a regular non-plated hole to tend to be generated improperly. Its a OrCAD PCB issue that if you simply close out the padstack designer, it doesn't save the actual .pad with warnings, if it had warnings. |

|

|

|

|

|

|

|

afyon

New User

Joined: 10 Mar 2014 Status: Offline Points: 12 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 11 Mar 2014 at 10:48am Posted: 11 Mar 2014 at 10:48am |

|

@Lekselius, I’m having the

same issue so I wanted to thank you for starting the thread. I worked around

the issue by making custom pads. Just for future reference, has this issue been

fixed now and if so, which revision number includes this update. I don’t have

an internet connection the PC I work on so I just wanted to know if the latest

patch would update this for me. I’m kind of hoping I can find a small update

patch instead of updating the complete OrCAD.

|

|

|

|

chrisa_pcb

Moderator Group

Joined: 29 Jul 2012 Location: San Diego Status: Offline Points: 772 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 10 Aug 2013 at 12:44pm Posted: 10 Aug 2013 at 12:44pm |

|

I'll be looking at fixing this issue shortly, but it probably won't make it into the tool until the next update in a couple of weeks.

|

|

|

|

d_nilsson

New User

Joined: 22 Jul 2013 Location: Sweden Status: Offline Points: 12 |

Post Options Post Options

Thanks(0) Thanks(0)

Quote Quote  Reply Reply

Posted: 26 Jul 2013 at 4:12am Posted: 26 Jul 2013 at 4:12am |

|

Ok, I will manually modify the padstack definition in Orcad PCB Designer then until Chris is back.

|

|

|

|

Tom H

Admin Group

Joined: 05 Jan 2012 Location: San Diego, CA Status: Offline Points: 6033 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 25 Jul 2013 at 5:41pm Posted: 25 Jul 2013 at 5:41pm |

|

The CAD interface programmer (Chris) is on vacation and will be back next week. |

|

|

|

d_nilsson

New User

Joined: 22 Jul 2013 Location: Sweden Status: Offline Points: 12 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 25 Jul 2013 at 4:55pm Posted: 25 Jul 2013 at 4:55pm |

|

Hi,

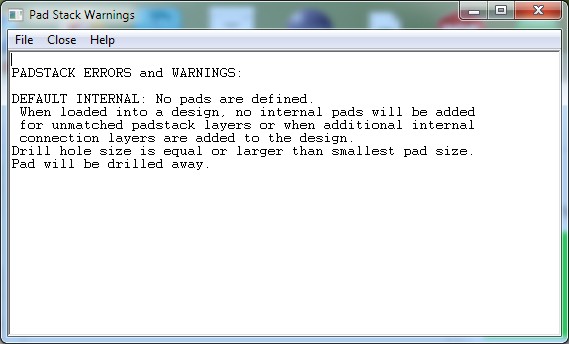

Was this issue ever resolved? I'm running into the same problem, using FP Designer in version 2013.08. If I open up the sample part AMPH_10-507143-85E in Sample Data - FP Designer.fpx and try to just build it (no changes) for Orcad PCB 16.6 the padstack definition for the NPTHs (keying holes using padstack c100hn295k395_395) is invalid. Cadence padstack editor will spit out during processing of the batch file: PADSTACK ERRORS and WARNINGS: Drill hole size is equal or larger than smallest pad size. Pad will be drilled away. I think this is since what FP Designer is telling Cadence to do is to add 1mm pads on all layers without thermal relief or anti-pad and then drill with a 2.95mm drill, Cadence doesn't like that definition of a NPTH. Is this a known bug? Any workarounds? According to padstack designer in FP Designer there should be a 3.95mm antipad, but that antipad seems to be set to "null" in Cadence when instead it maybe should have been the regular pad that should have been set to "null". Thanks Daniel |

|

|

|

BennsPCB

Advanced User

Joined: 30 Jan 2013 Location: Sweden Status: Offline Points: 98 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 15 Jun 2013 at 7:27am Posted: 15 Jun 2013 at 7:27am |

|

Have you turned on "Setup/Design Parameters.../Display non-plated holes".

Otherwise you only see the pad, which will be drilled away. Just my 2 cents, ... |

|

|

|

Lekselius

New User

Joined: 10 Apr 2013 Location: Sverige Status: Offline Points: 21 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 11 Jun 2013 at 10:57pm Posted: 11 Jun 2013 at 10:57pm |

|

I have watched the video and followed the exact same step as in the tutorial, creating an identical footprint but I get the same error when importing the footprint as I got previously.

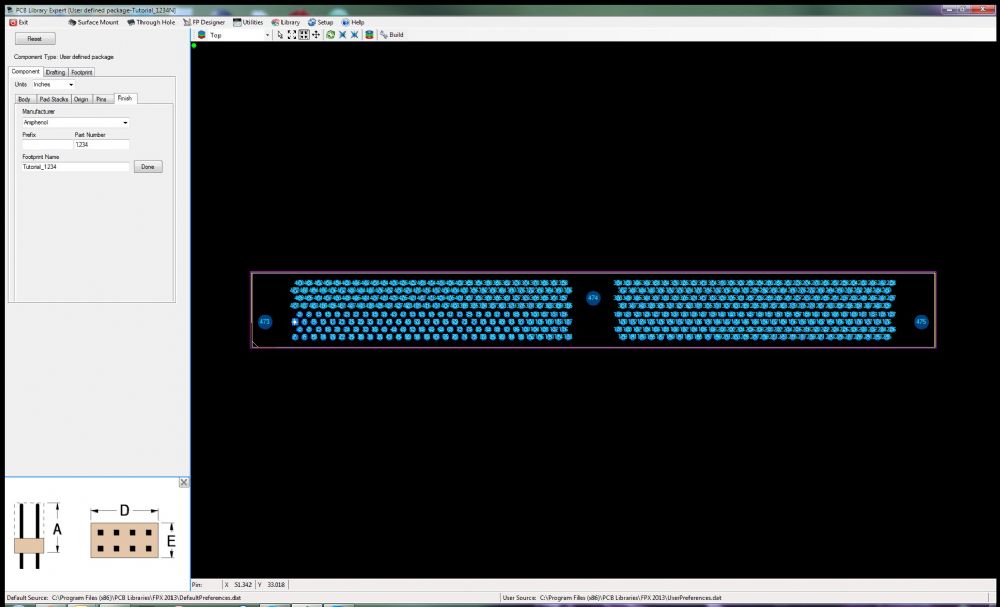

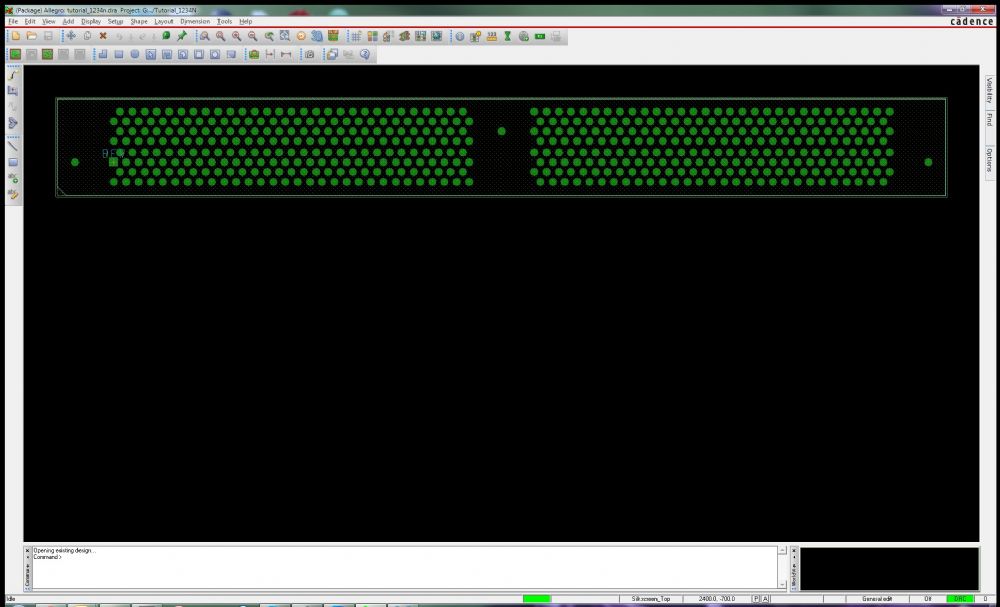

This is the footprint in package designer:  Error when running the batch file:  Resulting footprint in Orcad:  And the files to create the Orcad footprint created by FP designer: Tutorial_1234N.zip |

|

|

|

Tom H

Admin Group

Joined: 05 Jan 2012 Location: San Diego, CA Status: Offline Points: 6033 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 07 Jun 2013 at 7:03am Posted: 07 Jun 2013 at 7:03am |

|

Did you watch this Footprint Designer training video?

http://www.pcblibraries.com/products/fpx/userguide/default.asp?ch=104 http://www.pcblibraries.com/forum/pcb-library-construction-guidelines_forum30.html |

|

|

|

Lekselius

New User

Joined: 10 Apr 2013 Location: Sverige Status: Offline Points: 21 |

Post Options Post Options

Thanks(1) Thanks(1)

Quote Quote  Reply Reply

Posted: 06 Jun 2013 at 11:23pm Posted: 06 Jun 2013 at 11:23pm |

|

I'm running PCB Library Expert version 2013.02

|

|

|

|

Post Reply

|

Page 12> |

| Tweet |

| Forum Jump | Forum Permissions  You cannot post new topics in this forum You cannot reply to topics in this forum You cannot delete your posts in this forum You cannot edit your posts in this forum You cannot create polls in this forum You cannot vote in polls in this forum |